|

|

|

|

|

| 2013 년 새로운 아키텍처의 CPU "Hasewll" | |

이것은 Haswell가 Sandy Bridge (샌디 브리지)와 Ivy Bridge (아이비 브리지)와 마찬가지로 링 버스에서 가로로 CPU 코어와 GPU 코어와 노스 브릿지를 연결한 구조를 가지고있다는 것을 시사하고 있다. Intel의 현재 링 버스를 사용한 연결은 CPU의 모양은 유닛이 증가함에 따라 가로 방향으로 가늘고 길게되는 경향이있다.

아래는 Sandy Bridge와 Ivy Bridge의 다이로, Ivy Bridge는 GPU 코어와 시스템 에이전트 대형화만큼, 또한 가로로되어 있는지 알 수있다.Haswell도이 경향은 계속되는 것 같다. 그리고 Ivy Bridge보다 더 옆에 길고 된 것은, Ivy Bridge보다 GPU 코어와 노스 브릿지의 기능이 더욱 강화된 것을 보여주고있다.

|

| 아이비 다리 샌디 브릿지とのダイ PDF版애 이곳은 |

아래는 IDF에서 공개된 Haswell 칩 슬라이드와 실제 칩 비교이다. 양자는 거의 같은 형상을하고 있으며, 슬라이드의 Haswell 칩이 페이크가 아닌 실물임을 시사하고있다. 만약이 패키지가 37.5mm 코너 그렇다면, Haswell의 다이 크기는 약 180 ~ 190 평방 mm 정도라고하게된다. 그렇다하면 Haswell은 최근 Intel 메인 스트림 CPU로 비교적 작은 다이 크기의 CPU라는 것이된다.

|

| Haswellのチップ PDF版애 이곳은 |

|

| CPU의 die size 이행도 PDF 판은 여기 |

Intel은 메인 스트림 CPU 다이의 CPU 코어 수를 지금까지 1 코어에서 코어 2 (Merom), 4 코어 (Nehalem)로 늘려 또한 CPU 코어에 주변 기능의 통합도 노스 브릿지 (Nehalem)와 GPU 코어 (Sandy Bridge)와 진행 해왔다. 하지만 CPU 코어 수에 대해서는 여기에 와서 4 코어 멈출 기색을 보이고있다. Nehalem → Sandy Bridge → Ivy Bridge → Haswell, 메인 스트림 쿼드 코어 그대로 지연 전망이다.

대신 GPU 코어를 비롯한 주변 기능이 더욱 강화되거나 새로 추가되는 경향이있는 것 같다. 메인 스트림 CPU는 결국 범용 CPU 코어 수의 증가가 멈추고 대신 GPU 코어와 같은보다 성능 / 전력 효율적인 코어의 강화로 향하는 것으로 보인다. AMD는 이미 그 방향을 보여주지만, Intel 같은 노선으로 향한다. 아래는 Haswell 블록 추정 그림, 아마도 GPU와 노스 브릿지가 크게 강화될 것으로 보인다.

|

| Haswell 블록 다이어그램 PDF 판은 여기 |

|

| Ivy Bridge의 블록 다이어그램 PDF 판은 여기 |

|

| 샌디 브릿지のブロックダイアグラム PDF版애 이곳은 |

|

| 인텔 の Mooly 에덴 氏 (부사장, 일반 관리자 PC 클라이언트 그룹, 인텔) |

Intel은 2013 년 Haswell는 기존보다 압도적으로 배터리 구동 시간이 긴 노트북 PC를 만들려고하고있다. 따라서 2013 년 Ultrabook는 대기 전력을 현재의 20 분의 1로 인하.

"차세대 CPU의 Haswell는 20 배의 전력 향상을 도모한다. 오루데이 배터리 라이프를 실현할 수있는 무선 연결 상태 (적시 통신을) 대기 상태에서 10 일 이상 배터리를 유지하는 것도있다. 전원 에 연결 필요는 없다. 이것은 Intel 전력 최적화 실현된다. 전력 최적화는 우리는 에코 시스템 (장치 공급 업체)와 협력해야한다.하지만 믿고 싶어요. 너희 보는 무슨 을 여러분은 틀림없이 좋아하게 될 것이다. PC의 P는 개인에서 온 있지만, C는 앞으로는 창조성과 소비 : 소비 (전력)을 의미하게 될 것이다. "

인텔 の Mooly 에덴 氏 (부사장, 일반 관리자 PC 클라이언트 그룹, 인텔) は, 技術 カンファレンス "인텔 개발자

|

| 전압 레귤레이터 통합 |

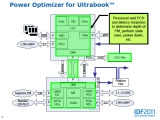

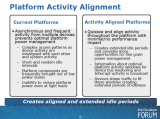

이전 보고서대로, Haswell의 노트 PC 버전은 메모리로 낮은 대기 전력 LPDDR3을 지원한다. 또한 화면에 변화가없는 경우 LCD 패널쪽에서만 새로 고침을 수행하여 CPU 측에서의 화면 데이터 전송을하지 않는다 패널자가 리프레시 (SPR)의 도입도 추진한다. 또한 전압 레귤레이터 (VR)를 온 다이 또는 온 패키지에 통합하는 개혁도 행한다고 볼 수있다.

그러나 이러한 장치 자체의 저전력화에 또한, Haswell 세대에서는 "CPPM"라는 플랫폼 전력 관리를 도입한다. Intel의 Eden 씨는, CPPM 이야말로 20 분의 1 대기 전력을 실현하기위한 열쇠라고 설명한다.

"전체의 개념은 CPU를 최대 절전 모드로두면, 배터리 구동 시간을 길게하는 것이다" "오늘의 주변 기기는 CPU를 비동기적으로 일으켜 버린다. 우리는 주변 장치에서 인터럽트를 압축 것으로, CPU를 더 긴 시간 절전 (스테이트)에두고 전력을 줄이기 위해 노력하고있다.이 방법으로 20 분의 1의 전력을 달성할 수있는 것 ""하지만 그러기 위해서는 많은 주변 기기 협력이 필요하다. 우리는 CPPM이 모든 길을 개척을 업계 전체에 전하려고하고있다 "(Eden 씨).

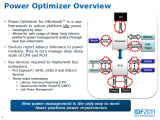

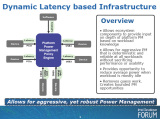

전력 최적화라고도 CPPM은 Haswell 플랫폼이다 "Shark Bay"전체 전력 제어 프레임 워크이다. Haswell을 탑재한 플랫폼 전체의 전력을 절감한다. Haswell와 "LynxPoint PCH"에 연결하는 장치 군 사이의 전력 관리를 행한다. Haswell과 LynxPoint는 전력 최적화를위한 플랫폼 전력 관리 컨트롤러가 탑재되는 것으로 보인다.

CPPM 프레임 워크의 기본 컨셉은 "Intel 이외의 구성 요소를 절전 아우에아하는"것이다. Intel은 자사가 제공하는 CPU와 칩셋 부분은 이미 상당한 수준까지 전력 절약 화를 달성했다고보고있다. 문제는 Intel CPU와 칩셋 이외의 부분에서 그곳을 개혁하지 않으면 노트 PC 전체의 전력 최적화가 이뤄지지와 Intel은보고있다. 아래의 슬라이드는 Intel이 IDF에서 나타낸 블루가 CPU의 전력, 레드가 시스템 전체의 전력을 보여주고있다.

|

| CPU 소비 전력 및 시스템 전체의 소비 전력 |

그리고 CPU 자체의 대기 아이돌 전력도 주변 장치의 최적화 아직도 낮출 수있다. 위의 그림을 보면 CPU의 전력도 일정 수준에서 내려 멈춰있는 것을 알고있다. 모바일 작업의 시간의 대부분을 차지하는 유휴 CPU와 칩셋의 전력은 시스템 전체의 협조가 없으면 낮출 수 없다. CPPM 프레임 워크의 초점은 여기에서있다. Intel는 주변 장치가 CPU에 자주 인터럽트와 DMA 액세스를 걸 덕분에 CPU가 오랫동안 절전 모드에 들어간 상태로있을 수없는 것에 문제가 있다고보고있다. 그래서 CPPM에서이 문제를 해결하려고하고있다.

|

| CPPM で 問題 を 解決 |

Intel의 Eden 씨는 장치와 OS에서 인터럽트가 절전에 얼마나 큰 영향을 미치는지를 다음과 같이 설명한다.

"오늘의 OS는 이른바 '틱 (tick) OS'이다. 일정주기 (tick)마다 OS가 타이머 인터럽트를 건다. OS가 인터럽트를 걸 때 CPU가 절전 (스테이트)에있을 경우, OS는" 자고있는가? "와 CPU에 얘기해 CPU를 절전 모드에서 일으킨다. 또한, 주변 기기, 예를 들어 프린터와 무선 LAN 등 모든 장치도 마찬가지로 인터럽트를 걸어 CPU를 일으킨다. 이 인터럽트가 CPU를 슬립 (스테이트)에서 일으켜 버리기 때문에, 배터리 구동 시간이 짧아지고 만다. "

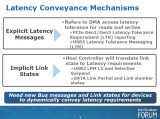

아래의 슬라이드는 CPU (와 칩셋)에 인터럽트와 DMA 액세스를 나타내고있다. 가로축은 시간 축에 수직으로 뻗어있는 화살표가 인터럽트와 DMA 액세스이다. 아래의 슬라이드에 그림이 현재의 플랫폼에서 본대로 수시로 인터럽트 및 액세스를 나타내는 화살표가 들어있다.

이러한 인터럽트와 DMA 액세스는 PCI Express 및 USB, SATA 등 인터페이스에 연결된 장치에서 들어간다. 각각의 인터럽트와 DMA 액세스는 동기화하지 않고, 시간 축에 완전히 분산되어있다. 각 인터럽트와 DMA 액세스 번에 CPU 측의 일부 장치가 절전 모드에서 활성으로 되돌려 버린다. 복잡한 인터럽트와 DMA 위해, CPU의 유휴 시간은 나뉘어화된 불연속 짧은 유휴 시간에되어 버린다.

|

| 인터럽트와 DMA 액세스 |

절전 스테이트은 깊으면 깊을수록 전력을 줄일 수 있지만, 대신 복귀 지연 시간이 길어진다. 따라서 깊은 절전 스테이트를 충분히 활용하려면 어느 정도의 유휴 시간을 지속하지 않으면 어렵다. 유휴 시간이 나뉘어되어 있으면 CPU 전체 깊은 절전 스테이트에 들어갈 수있는 기회가 매우 제한되어 버린다. CPU 측이 깊은 절전 스테이트 전력을 제공하고, 그것에 의해 전력을 줄일 기회가 꽤 손실되고있는 상황이다.

그래서 아이디어로 인터럽트와 DMA 액세스를 정리하여 버스트하고 버리는 방법이 떠오른다. 인터럽트와 DMA 액세스에는, 실은 타이밍 중요하지 않은 것이나 장치 측에 버퍼함으로써 지연시킬 수있는 것이 존재한다. 위의 슬라이드에서 화살표는 인터럽트와 DMA 액세스 유형 분류되고있다.

위의 슬라이드 블랙 화살표는 OS의 타이머 인터럽트이지만, 이것은주기적인 이동할 수 없다. 오렌지는 중요한 인터럽트 이것도 타이밍을 늦추는 것이 없다. 보라색은 중요한 데이터 트래픽, 이것도 타이밍을 움직일 수 없다. 반면 블루 시기를 뒤로 늦추는 것이 가능 인터럽트, 그린도 마찬가지로 지연시킬 수있는 데이터 트래픽을 나타내고있다. 그림에서 타이밍을 지연시킬 수있는 화살표가 상당수 나타나고있다.

그래서 중요한 인터럽트 및 액세스 타이밍 그대로 지연이 가능한 인터럽트 및 액세스 중요한 타이밍에 맞춰 (아라하고) 정리한 처리 해 버린다.

이러한 조정을 행한 것이 위의 슬라이드 중 아래의 그림이다. 각 인터럽트와 DMA가 어느 정도의 입도 버스트로 정렬이되고있다. 따라서 인터럽트 사이의 완전히 아이돌 시간이 이전보다 훨씬 오래 가지고 있는지 알 수있다. 이 "아이돌 윈도우"가 충분히 넓은하면 CPU는 깊은 절전 스테이트에 들어가 전력을 크게 줄일 수있게된다. 아래의 슬라이드는 인터럽트와 DMA 액세스를 아라하고 아이돌 윈도우를 펼치는 개념을 나타낸 그림이다.

|

| 인터럽트를 파열 그림 |

각 장치의 인터럽트와 DMA 액세스를 아라하기 위해서는 지금까지없는 구조가 필요하다. CPU / 칩셋 측의 CPPM 컨트롤러가 각 장치마다 인터럽트와 DMA 액세스를 얼마나 지연 시켜도 괜찮은를 잡아 필요가있다. 장치가 허용되는 시간 이상 지연시켜 버리면, 안전한 동작을 할 수 없게되거나 성능이 소가되기도 버린다. 어디 까지나 각 장치의 허용되는 범위에서 인터럽트와 DMA 액세스를 아라해야한다. Eden 씨는 다음과 같이 비유한다.

"먼저 CPU와 시스템은 각 장치에 최대 지연 시간, 즉 인터럽트를 걸고 응답까지 기다릴 최대 시간을 묻는 장치는 각각 허용 가능한 지연 시간을, 예를 들면 400us (마이크로초) 또는 500us, 600us이라고 대답 다음 칩셋이 인터럽트를 받으면 칩셋은 "CPU는 대기 상태이므로 나중 400us 복귀시킬 수 없다"고 장치에 전한다. 그리고 일정 시간이 지난 후 CPU를 복귀시켜 모든 인터럽트에 대한 응답을 동시에 행하게 "

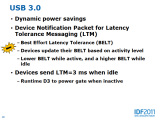

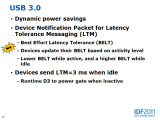

Intel은 지연의 전달 등을 위해 장치와 CPU 사이에 새로운 버스 및 프로토콜을 개발했다. 지연의 허용치를 동적으로 컨트롤러에 전달하기위한 "Latency Tolerance Reporting (LTR)"나 "Latency Tolerance Messaging (LTM)"를 정의. PCI Express 및 USB 같은 업계 표준 규격을 그들의 스펙을 도입하게 움직여왔다. 또한 지연 시간을 허용하도록하기 위해보다 지능적인 버퍼 시스템 장치 칩 측에 탑재하는 것도 요구하고있다. 또한 버퍼링을 핸들하기위한 "Opportunistic Buffer Flush / Fill (OBFF)"을 정의했다.

|

|

|

|

|

|

|

|

|

| 지연 허용치 등을 동적으로 컨트롤러에 전달하기위한 프로토콜 등을 책정했다 | ||

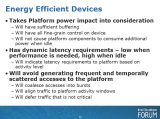

실은, Intel은 CPPM의 구조를 몇 년 전에 이미 제안하고있다. 이 기사에서 사용하는 슬라이드의 대부분도 2008 ~ 2009 년 IDF의 것이다. 같은시기에이 기술을 계몽하기 위해 "Energy - Efficient Platforms"라는 백서도 내놓고있다. 관련 특허도 같은시기에 출원되고있다. 즉, 기술의 기본적인 골격은 사실 3 년 전부터 잘 된 셈이다. 그러나 실제로 구현되는 것은 구상에서 5 년 뒤인 2013 년부터이다.

그만큼의 기간이 필요할는 것이 Intel 1 사에서 처리되는 문제가 아니라 업계 전체를 침몰 필요가 있었기 때문이다. PCI Express 및 USB 등 다양한 인터페이스 연결 장치에 CPPM의 전력 최적화의 개념에 따라달라고 필요가있다. 반대로 말하면, 계몽 활동을 계속하고 5 년, 드디어 프레임 워크를 완성하는 요소가 갖추어지고있는 것 같다.

는 CPPM 프레임 워크 Haswell는 어디까지 낮출 수있는가? 아래는 LTR를 사용하여 CPU / 칩셋에 전달 지연 허용 시간을 뻗어 나갔다 경우의 유휴 전력을 비교 슬라이드이다. 이것을 보면, 100us 지나서 근처로부터, 이마 계속 소비 전력이 떨어지는 것을 알 수있다. 백서는 유휴 시간에 대한 지연 시간은 최소 300us 바람직하다고하고있다.

|

| 지연 허용 시간을 늘려 나갔다 경우 아이돌시의 소비 전력 |

Intel의 CPPM의 구상이 실현되면, 노트북 PC의 유휴 시간 평균 소비 전력은 현재보다 크게 떨어질 가능성이 높다. 이에 패널 셀프 리프레 쉬나 LPDDR3이 더해지면 Ultrabook 평균 전력은 극적으로 낮출 수있을 것 같다. 대기 전력을 낮출 수 있기 때문에 휴대 전화와 같이 하루 종일 작동시킨 상태에서 무선을 통해 메일 등을 수신하면서 장시간 구동시키는 것이 가능하게된다.

또 다른 견해를하면, 이것은 전력에 대해 일체의 고려가 없었던 시대에 만들어진 인터럽트 아키텍처에 대한 개혁의 첫 번째 단계이기도하다.

'IT > computer' 카테고리의 다른 글

| Desktop CPU LineUP (Intel, AMD) (0) | 2012.01.19 |

|---|---|

| ReFS - Windows 8 의 새로운 파일 시스템. (0) | 2012.01.18 |

| (tip)크롬에서 화면 정지시키기 (0) | 2011.07.28 |

| (tip)크롬 브라우저에서 마그넷 링크 사용하기 (How to open 'Magnet Link' in Chrome browser?) (0) | 2011.07.19 |

| 웹 브라우저의 간단한 역사. (0) | 2011.04.14 |